# Unified Address Translation for Memory Mapped SSDs with FlashMap

#### **Jian Huang**

Anirudh Badam<sup>†</sup>

Moinuddin K. Qureshi

Karsten Schwan

### Bridging the DRAM-Disk Gap

Application Memory Component

Application Storage Component

### Bridging the DRAM-Disk Gap

Application Memory Component

Application Storage Component

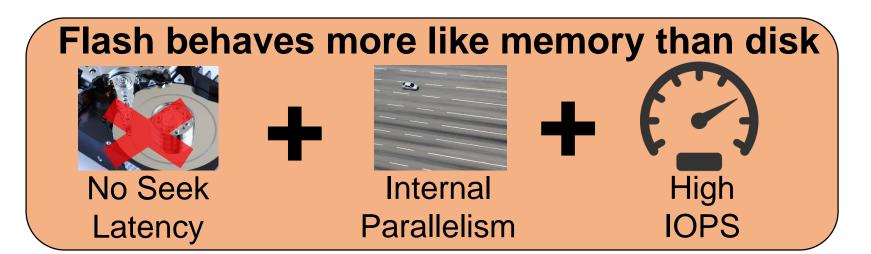

Flash behaves more like memory than disk

#### Flash behaves more like memory than disk

#### Flash behaves more like memory than disk

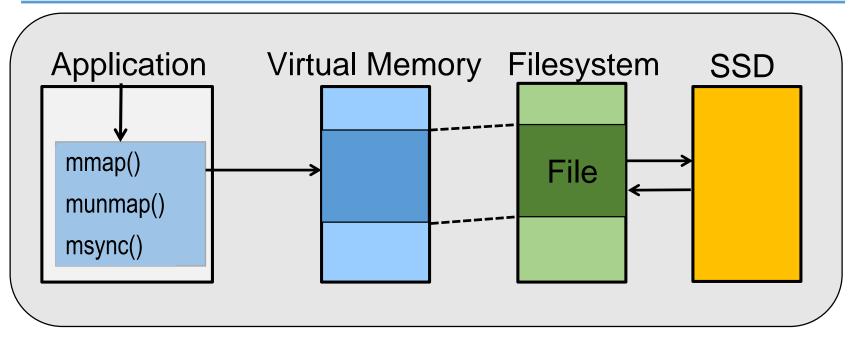

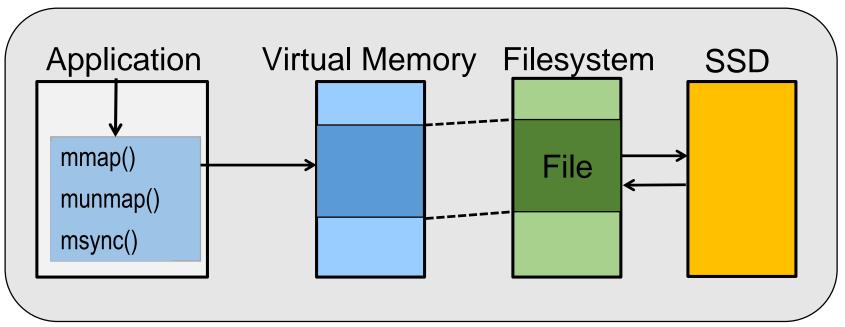

#### Use Flash as Memory [Badam et al., NSDI'11]

Application Storage Component

#### Use Flash as Memory [Badam et al., NSDI'11]

Application Memory Component

Application Storage Component

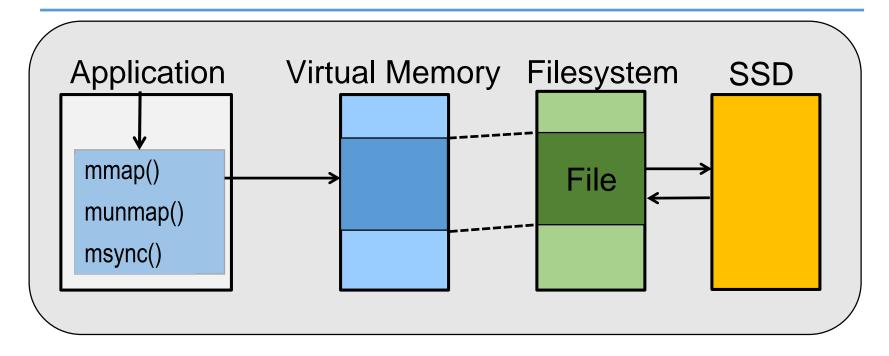

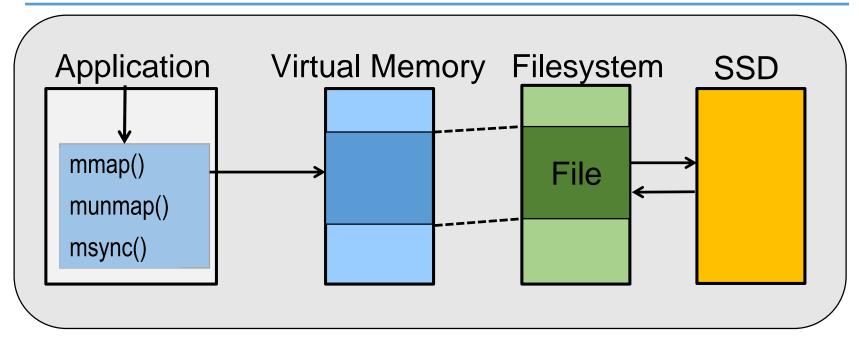

Extended Memory

Minimal Code Modifications

Data Durability

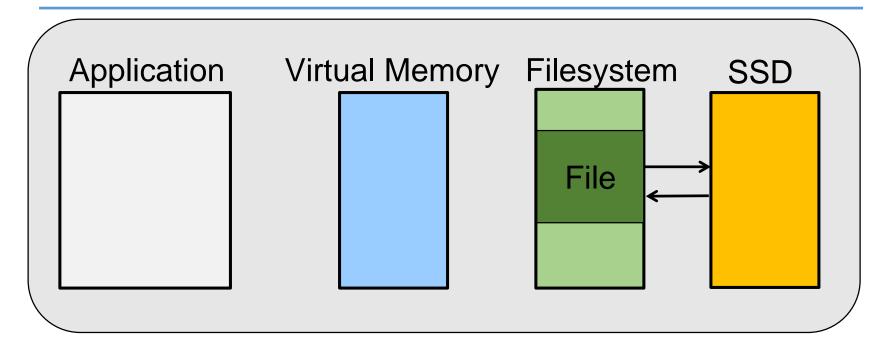

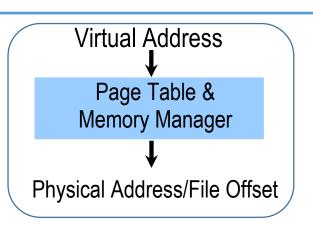

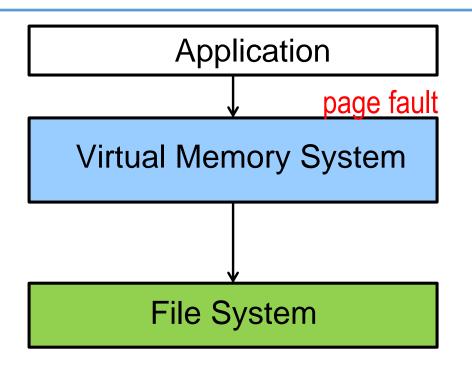

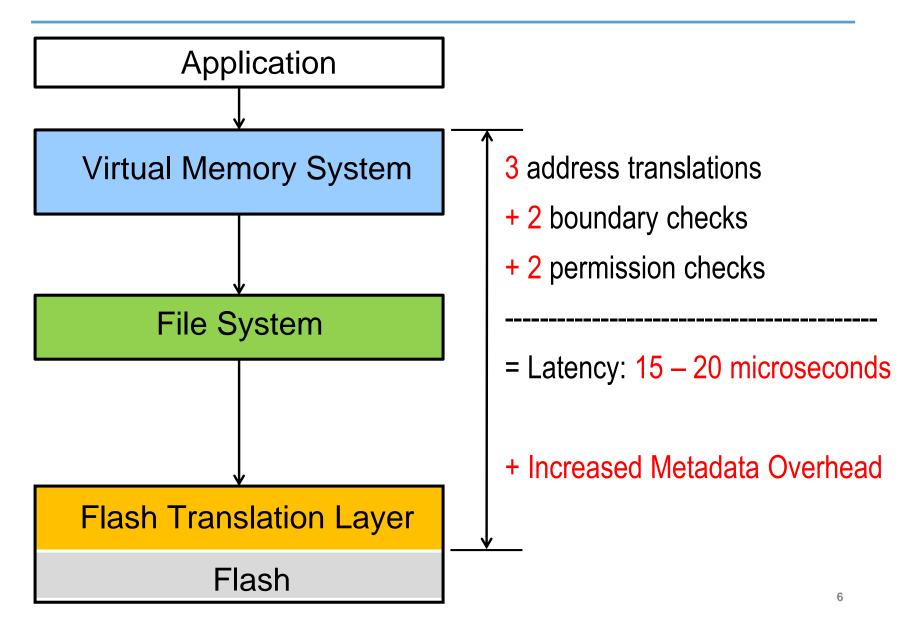

**Application**

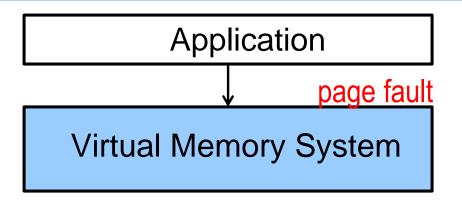

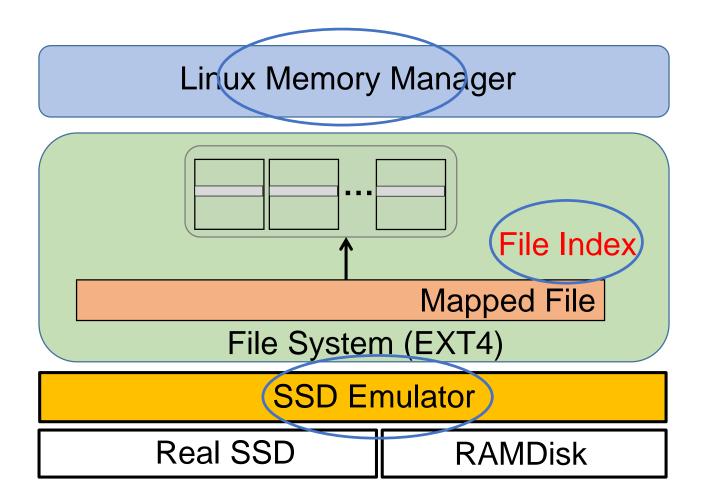

Virtual Memory System

File System

Flash Translation Layer

Flash

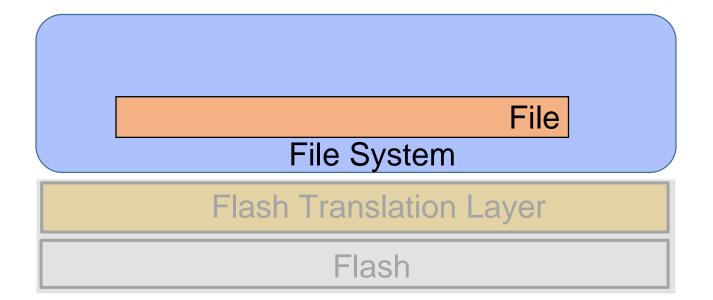

File System

Flash Translation Layer

Flash

Flash Translation Layer

Flash

#### Software Overhead Quantified

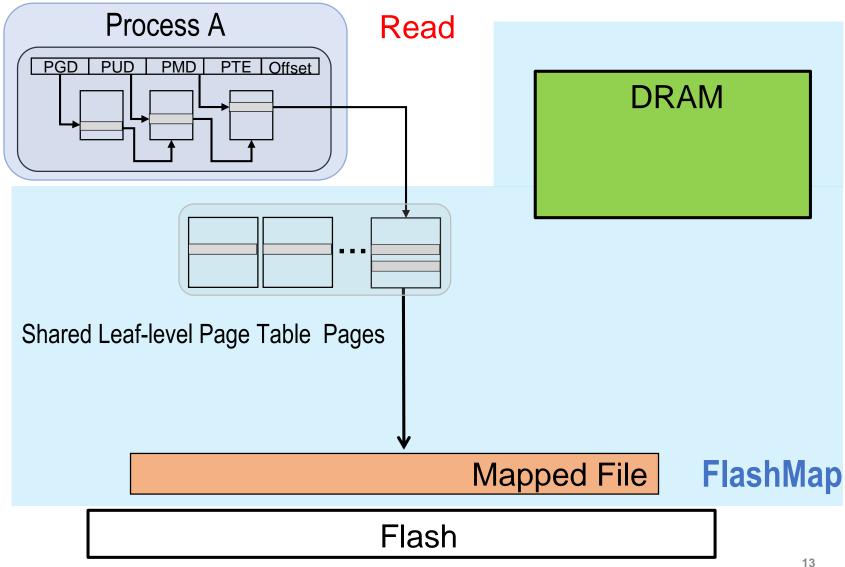

#### FlashMap: Unified Address Translation

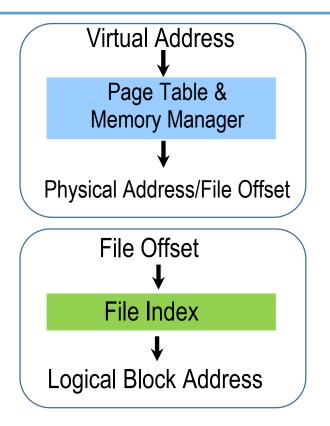

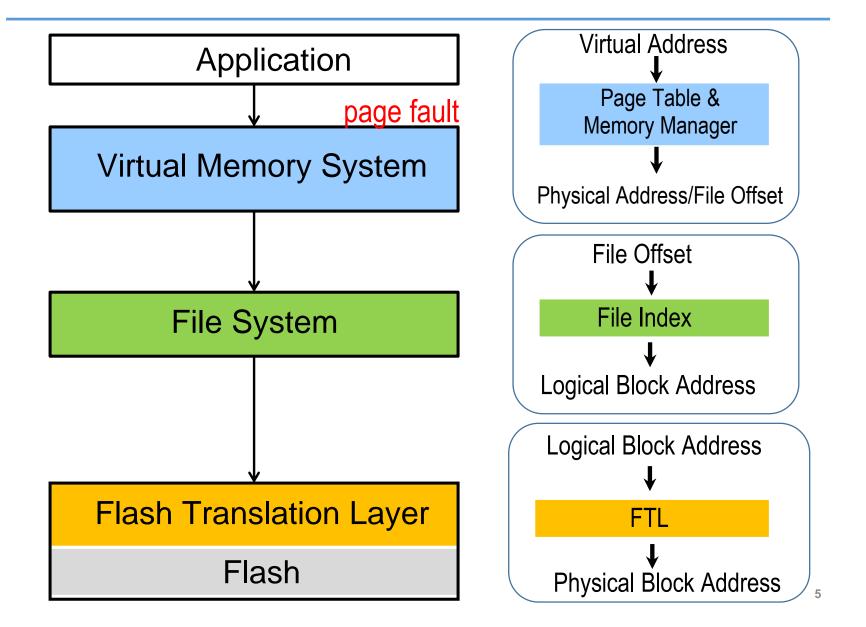

Application

Virtual Memory System

File System

Flash Translation Layer

Flash

- 1 Reduced Storage, only 1 mapping table

- 2 Reduced Latency, only 1 address translation + 1 permission check +1 boundary check

#### FlashMap: Unified Address Translation

**Application**

Unified Address Translation

Flash

- Reduced Storage, only 1 mapping table

- Reduced Latency, only 1 address translation

+ 1 permission check +1 boundary check

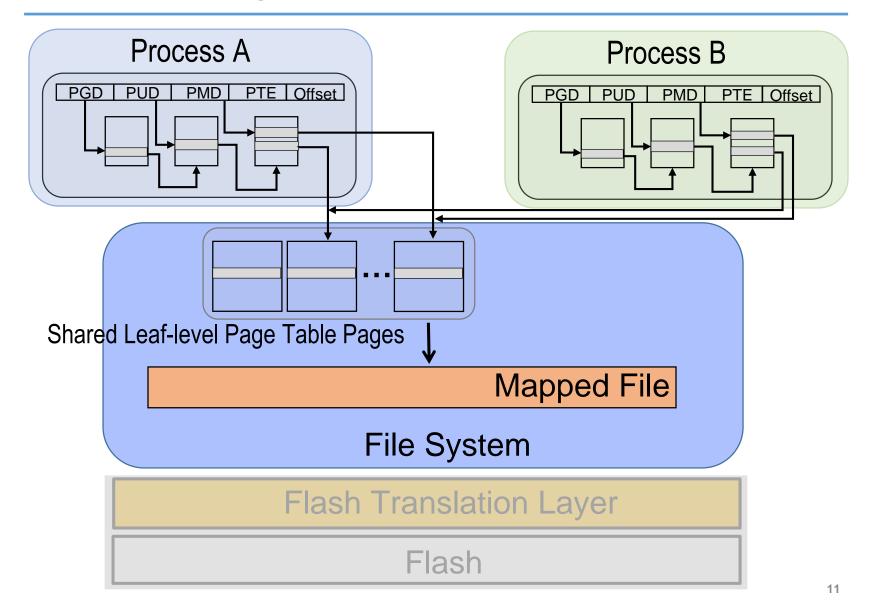

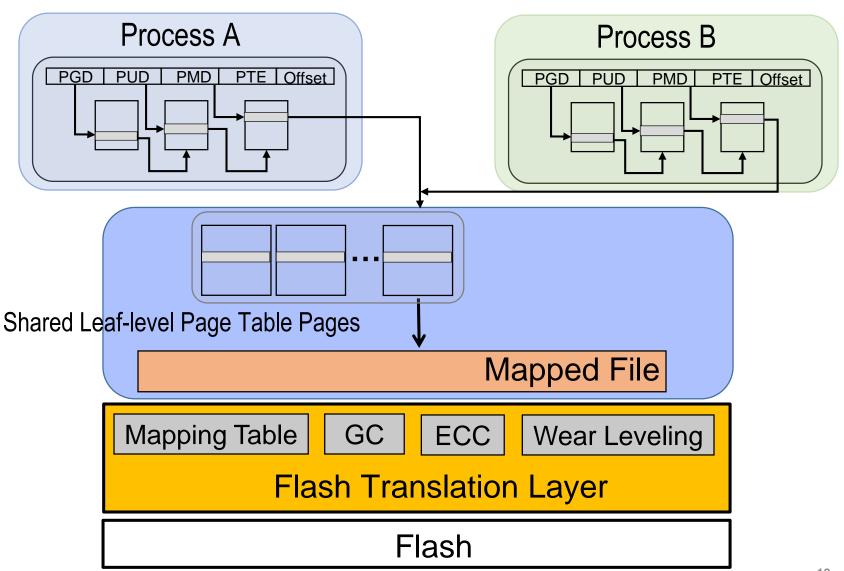

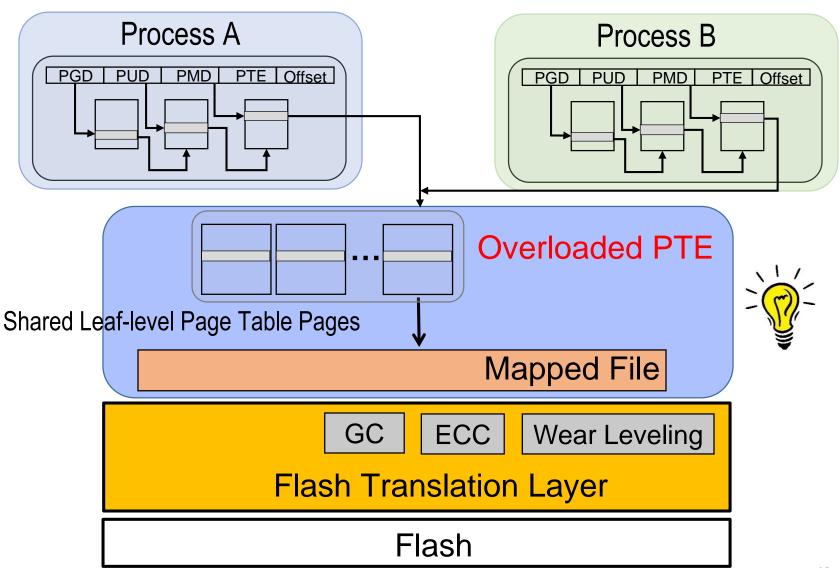

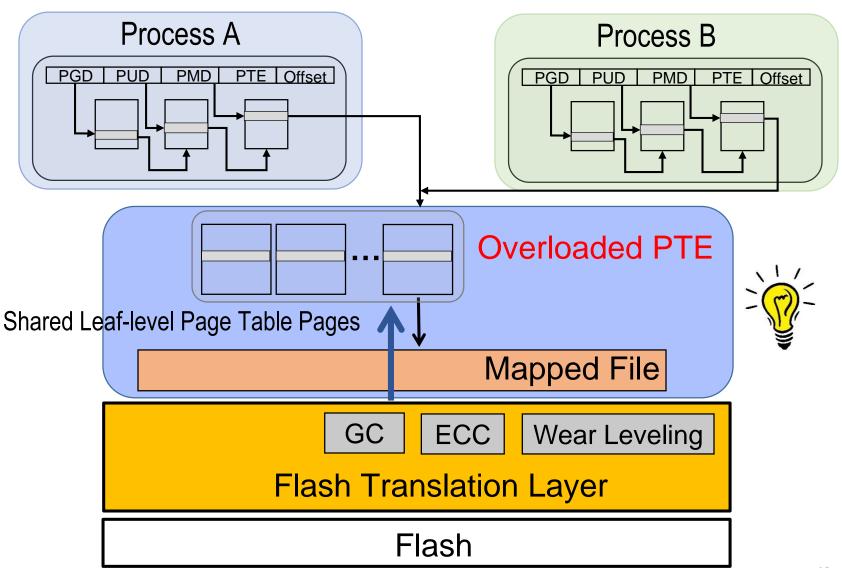

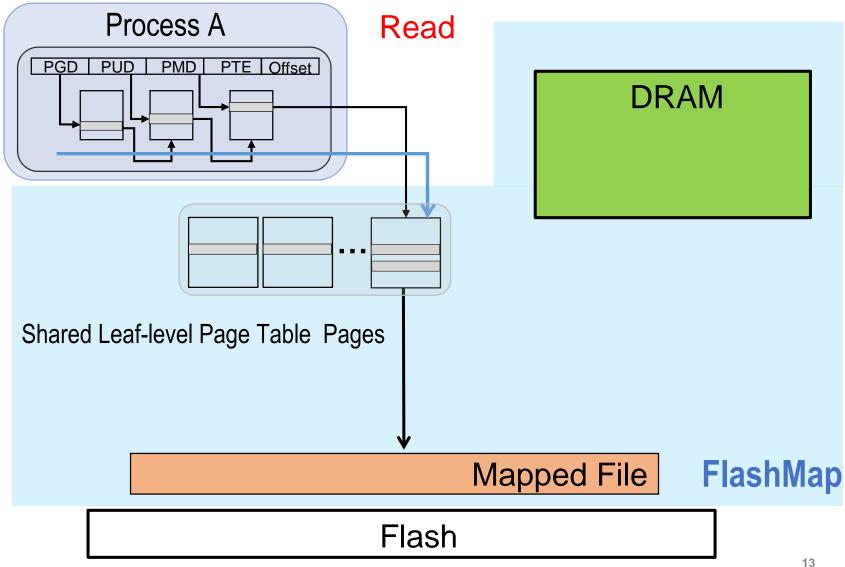

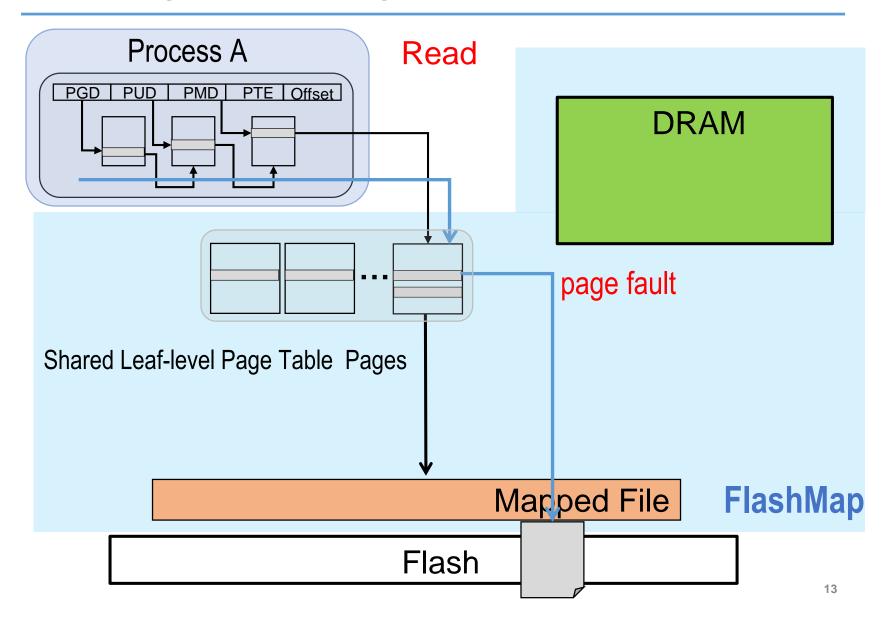

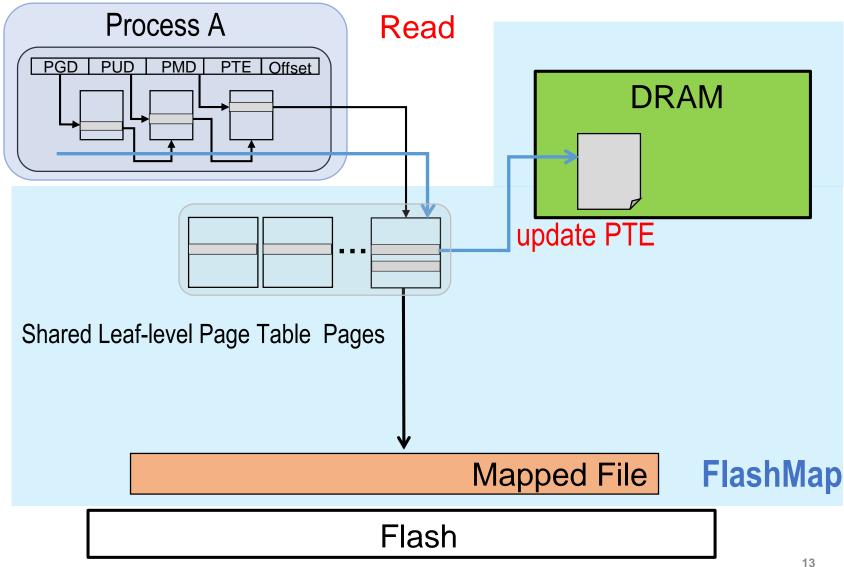

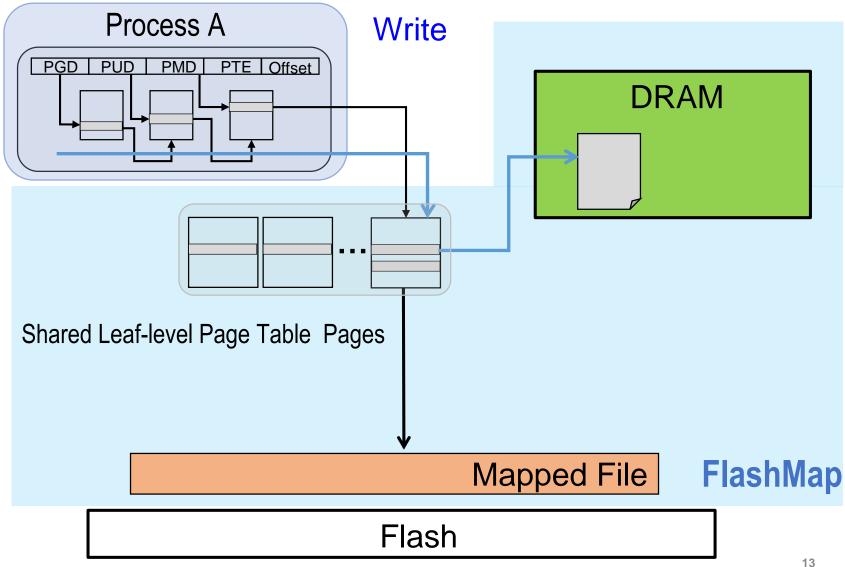

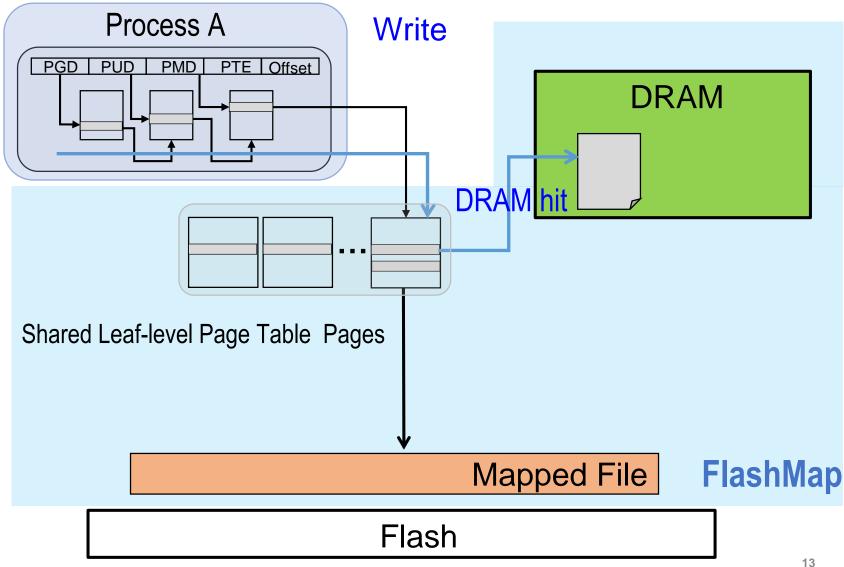

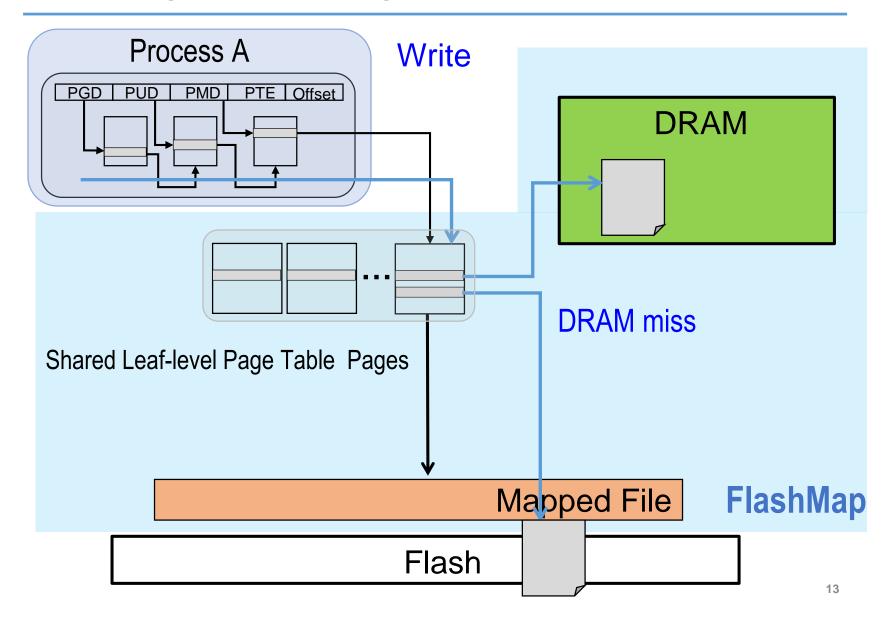

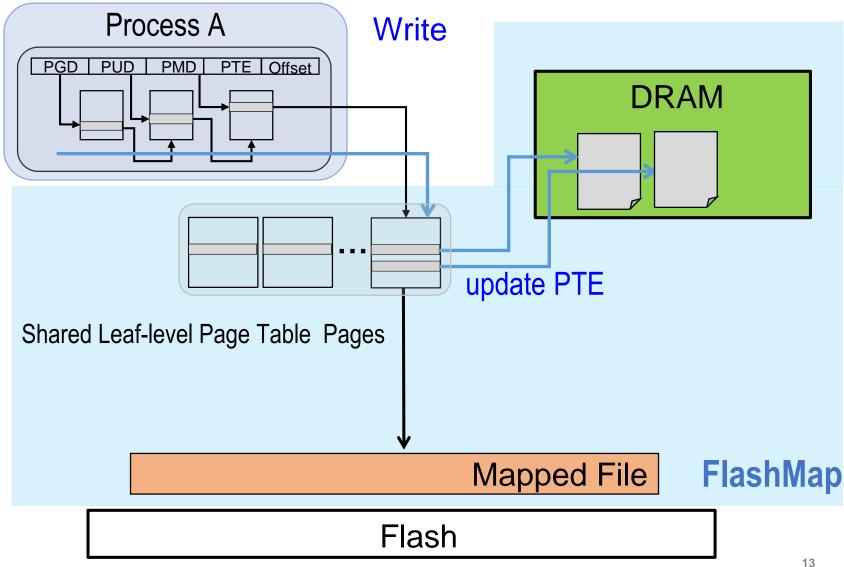

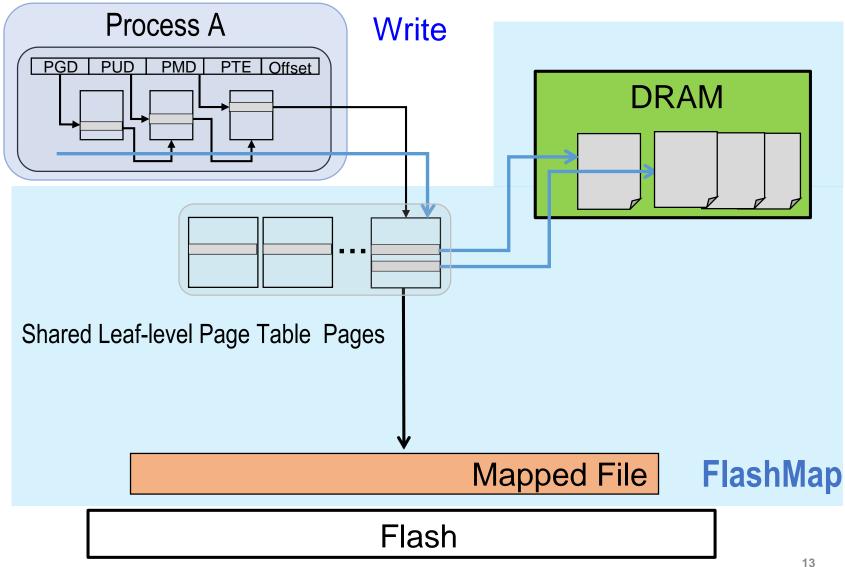

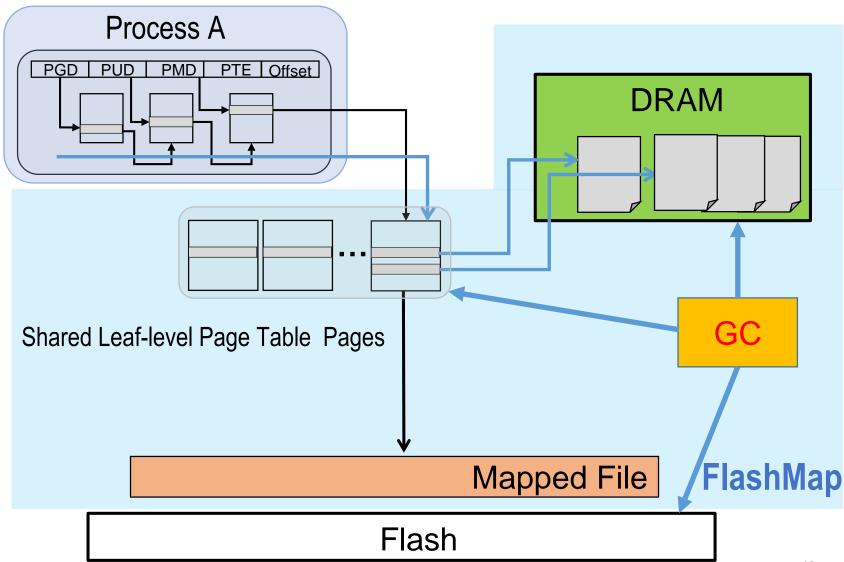

Process A

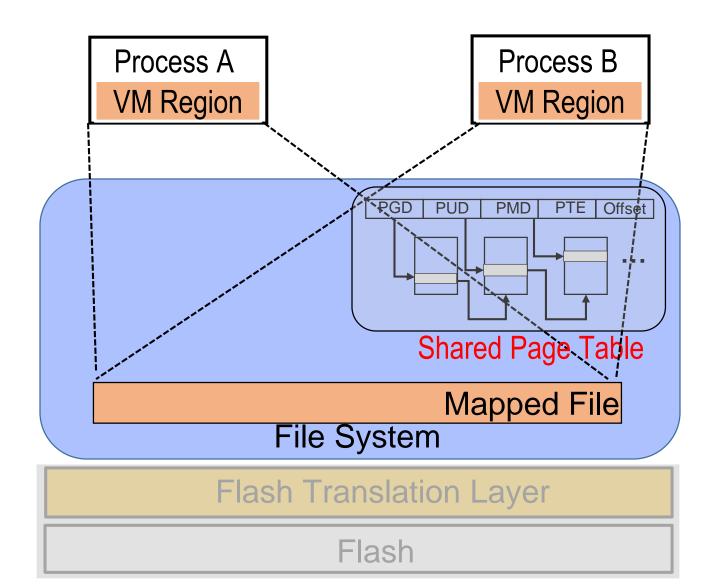

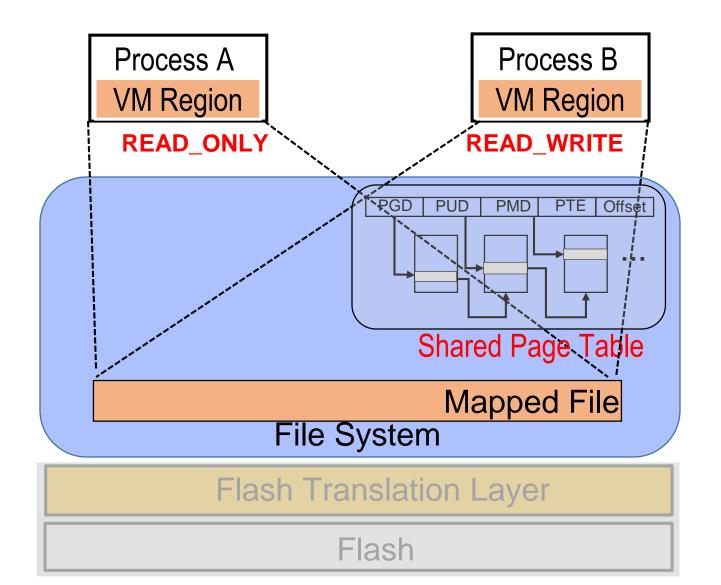

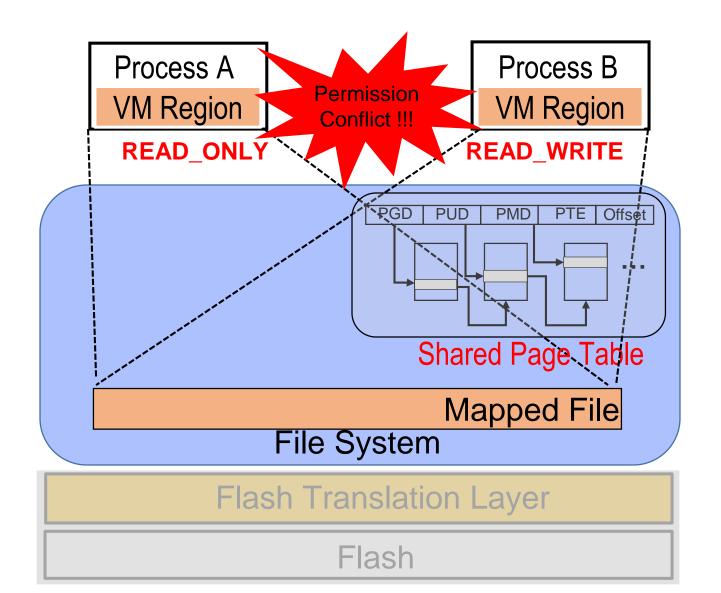

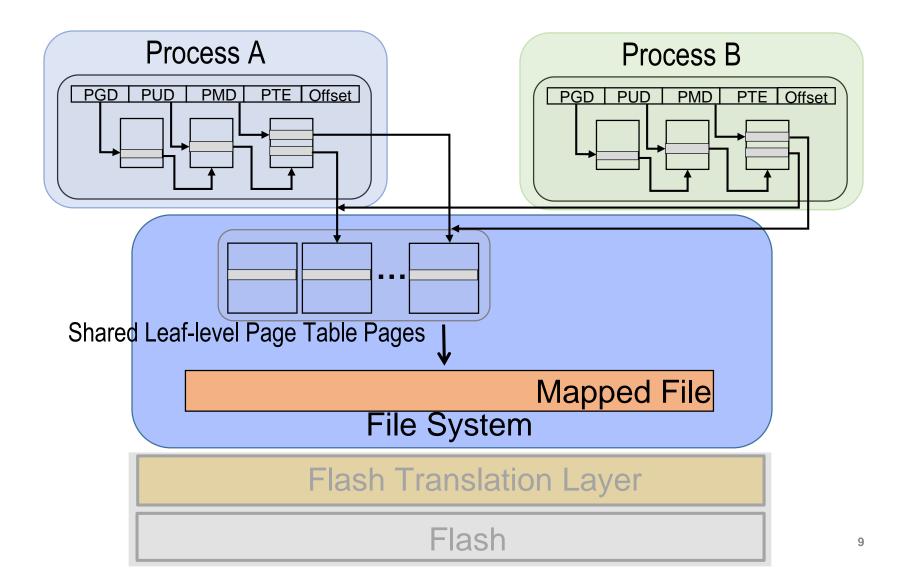

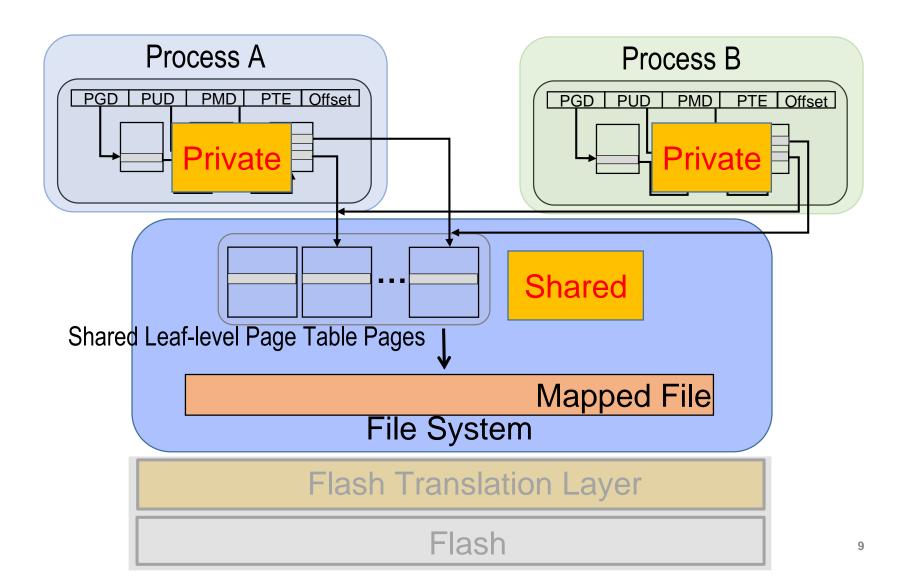

Only share the leaf-level page table pages! Process B Process A VM Region **VM** Region **READ\_ONLY** READ\_WRITE PGD PUD PTE Offset PMD Shared Page Table Mapped File File System Flash Translation Layer Flash

Only share the leaf-level page table pages! Process B Process A VM Region **VM** Region **READ\_ONLY** READ\_WRITE PGD PUD PTE Offset PMD Shared Page Table Mapped File File System Flash Translation Layer Flash

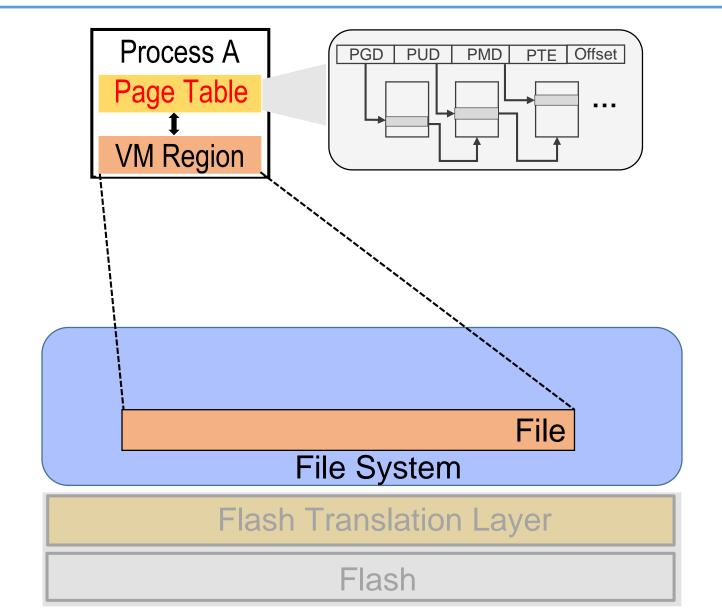

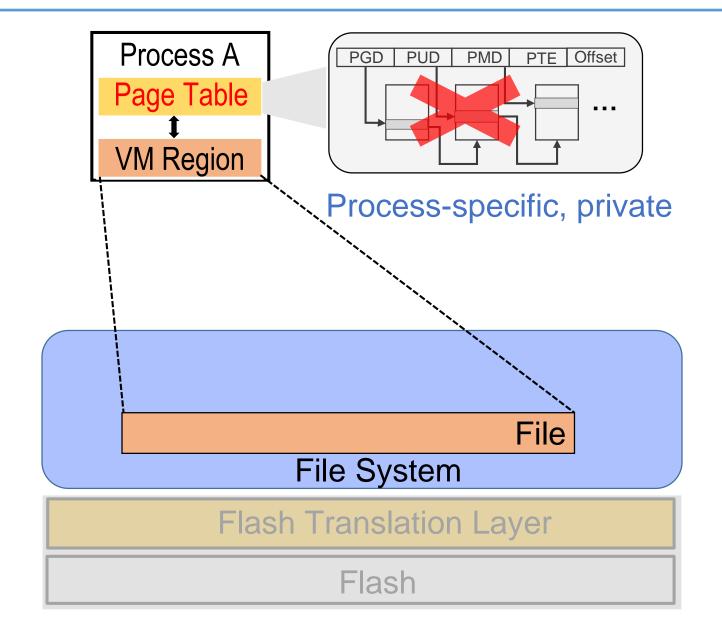

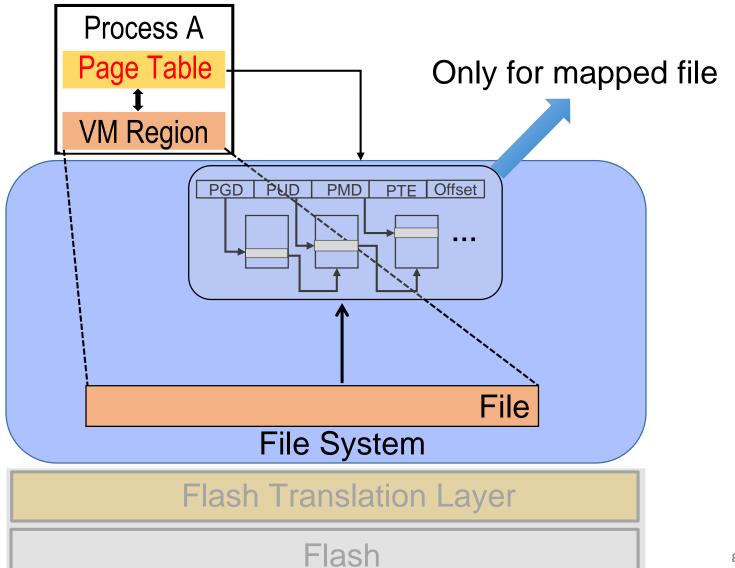

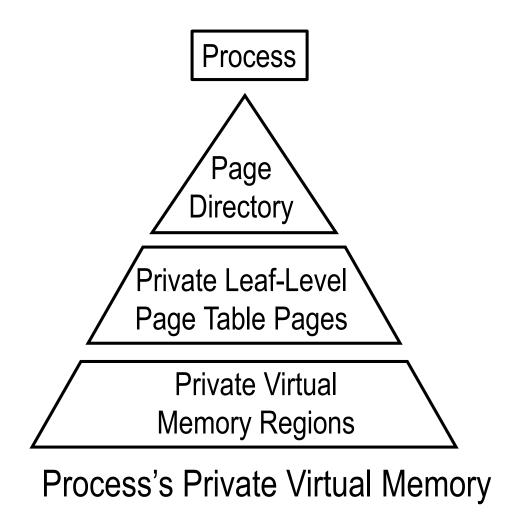

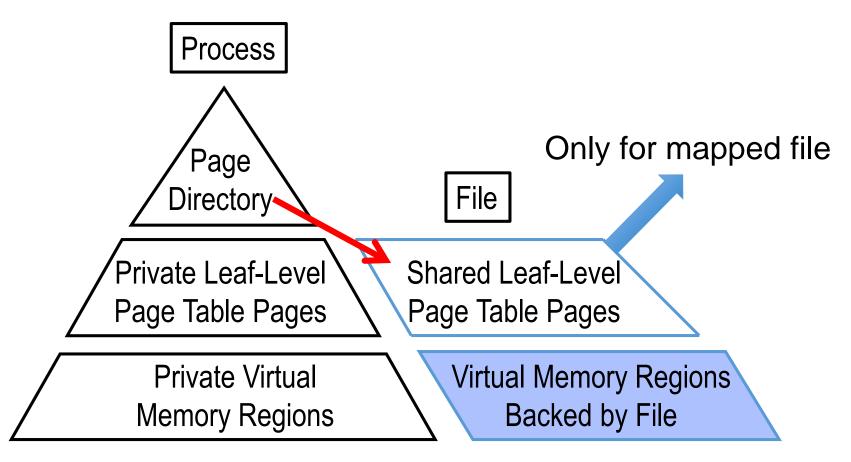

### Page Table in FlashMap

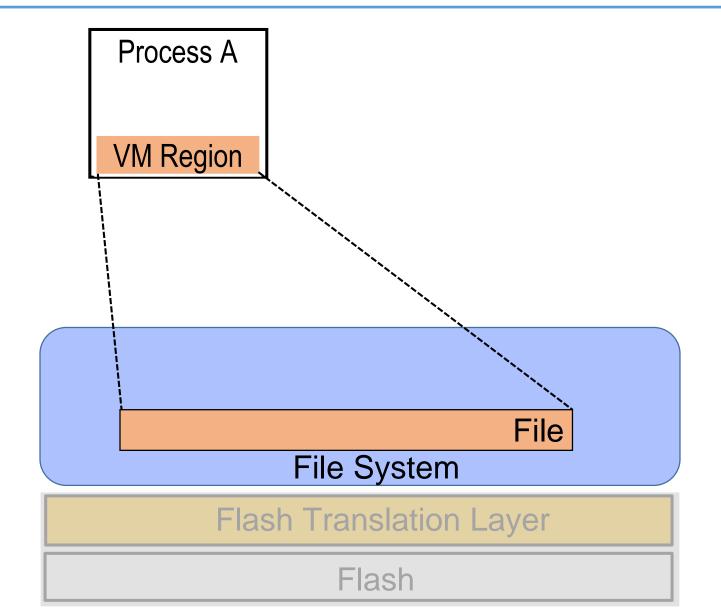

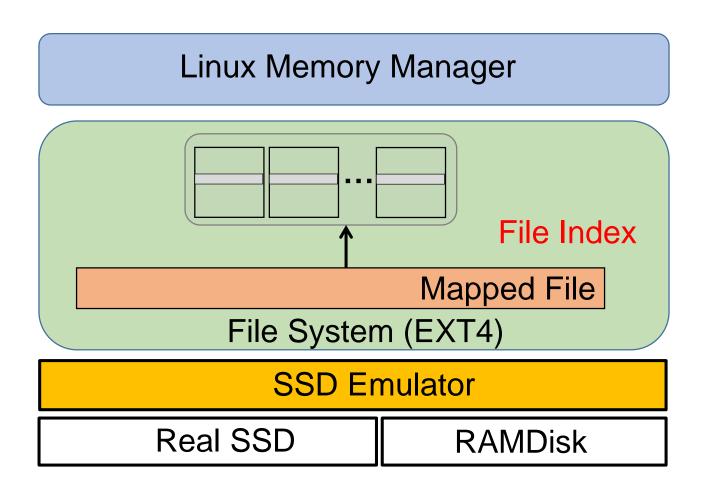

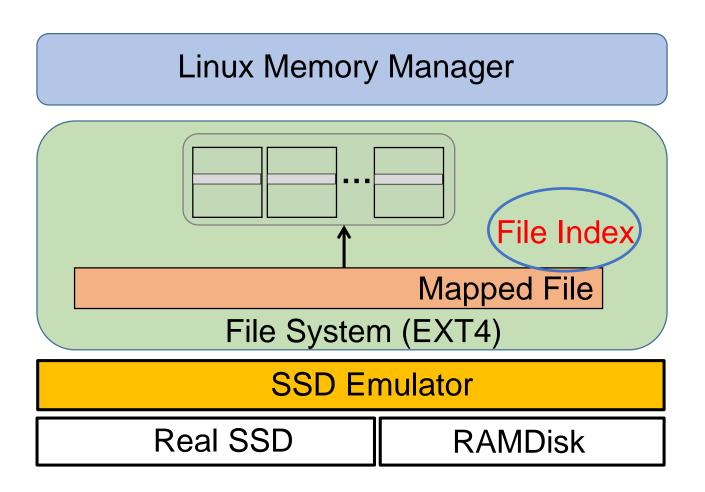

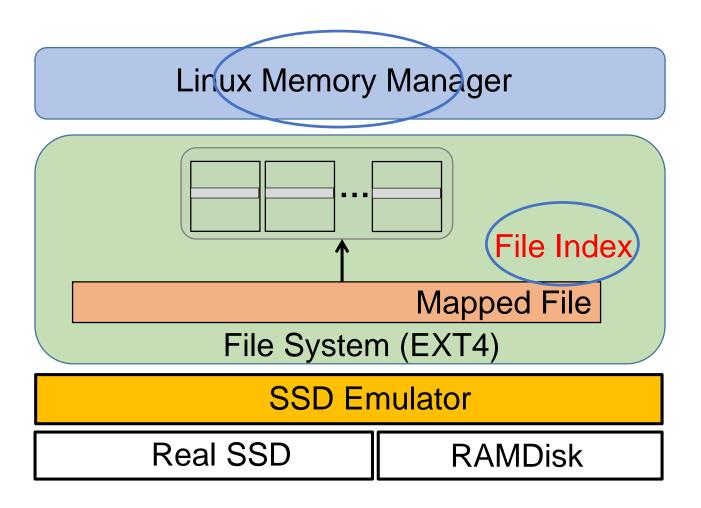

Before Mapping a File

### Page Table in FlashMap

Process's Private Virtual Memory + File Backed Memory

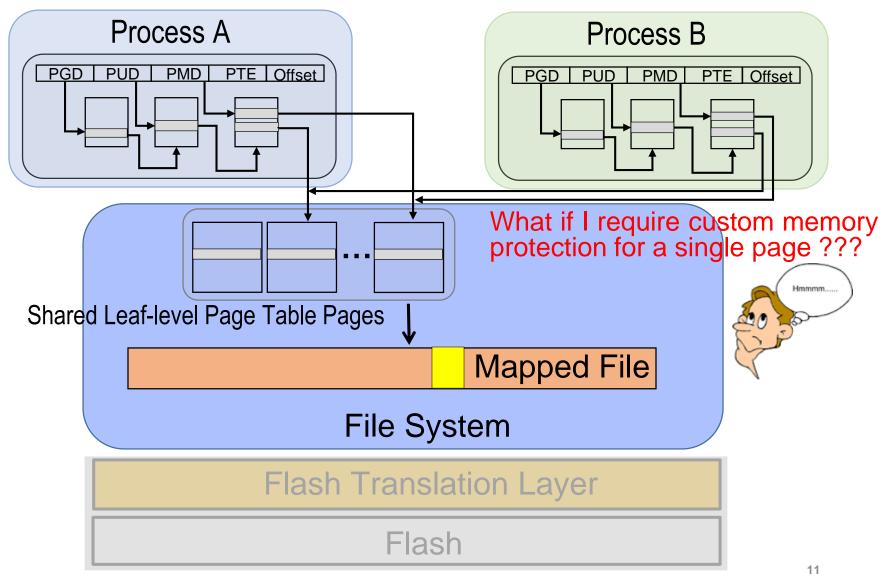

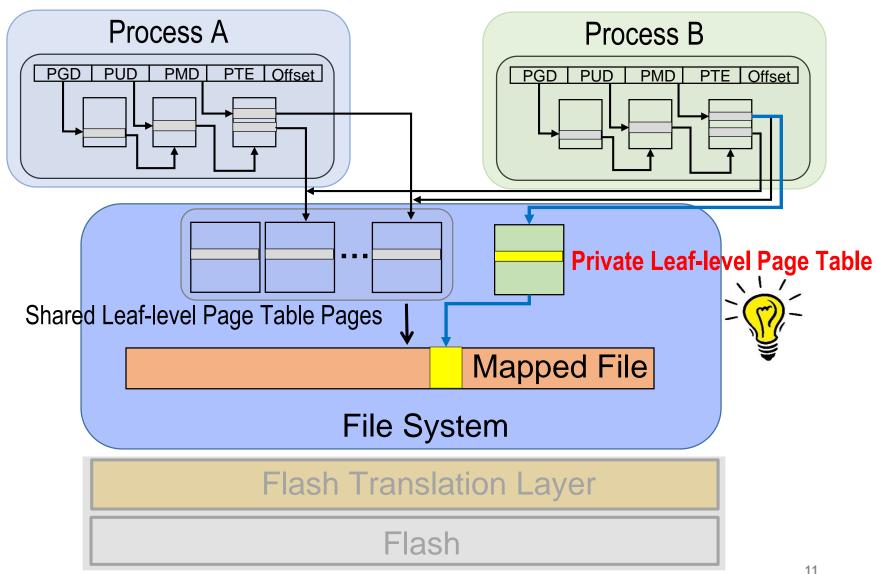

# Preserving Memory Protection

# Preserving Memory Protection

### Preserving Memory Protection

### Combining FTL and Shared Page Table

### Combining FTL and Shared Page Table

### Combining FTL and Shared Page Table

### Experimental Setup

Intel Xeon processors + 64 GB DRAM + 2 TB SSD

| Baseline | unmodified Linux:<br>mmap + EXT4 + FTL with page-level mapping |

|----------|----------------------------------------------------------------|

| FTL+FS*  | mmap + combined FTL & file system                              |

| FlashMap | unified address translation                                    |

<sup>\*</sup>similar to Nameless Writes [Zhang et al., FAST'12] and DFS [Josephson et al., FAST'10]

### Real Application Workloads

| NoSQL Store     | + W YCSB redis              |

|-----------------|-----------------------------|

| SQL Database    | Shore-MT + TPCC, TPCB, TATP |

| Graph Analytics | + PageRank<br>GraphLab      |

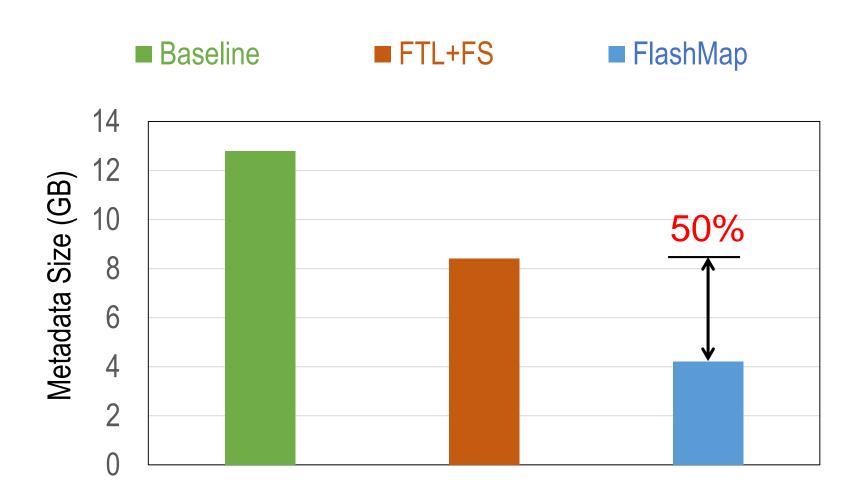

#### Metadata Size for 2 TB SSD

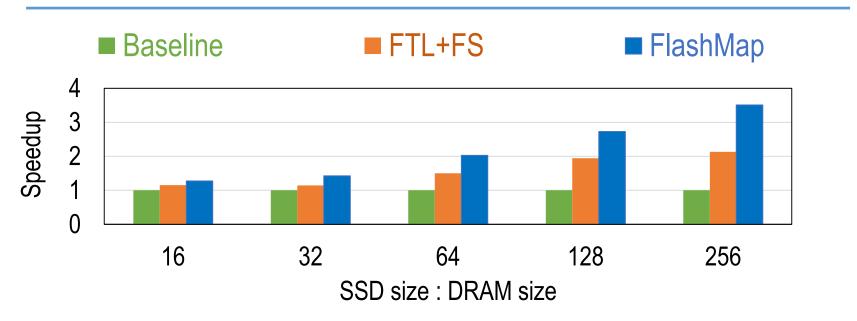

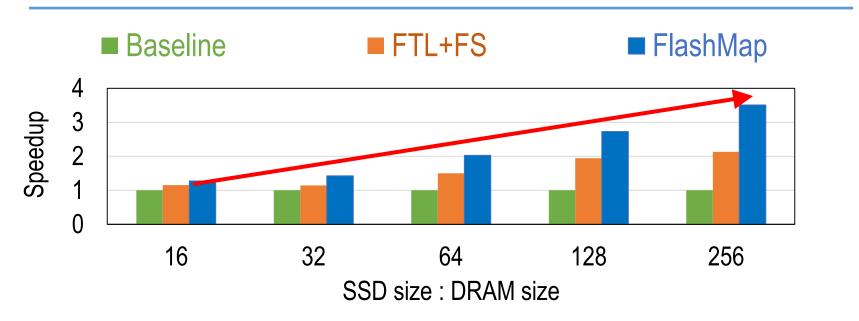

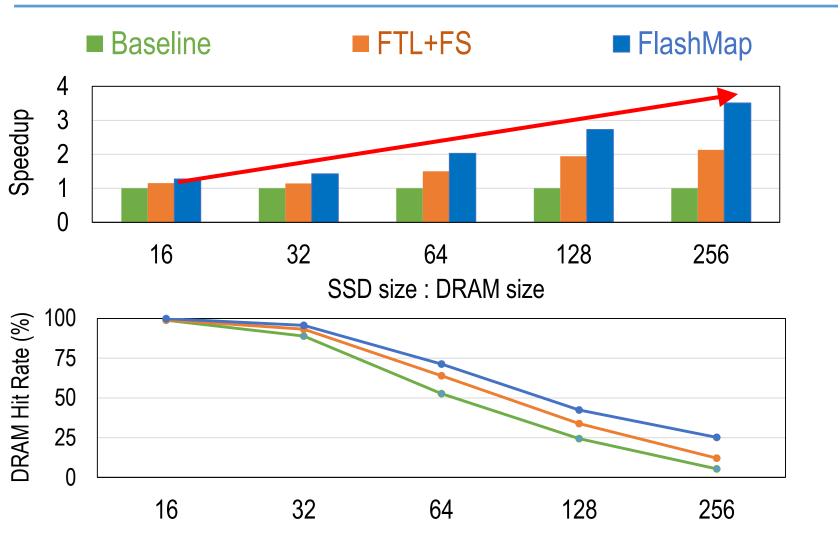

#### Benefits from Reduced Mapping Overhead

FlashMap: 1.7x performance improvement over FTL+FS

#### Benefits from Reduced Mapping Overhead

FlashMap: 1.7x performance improvement over FTL+FS

#### Benefits from Reduced Mapping Overhead

Reducing the mapping overhead improves the DRAM caching efficiency

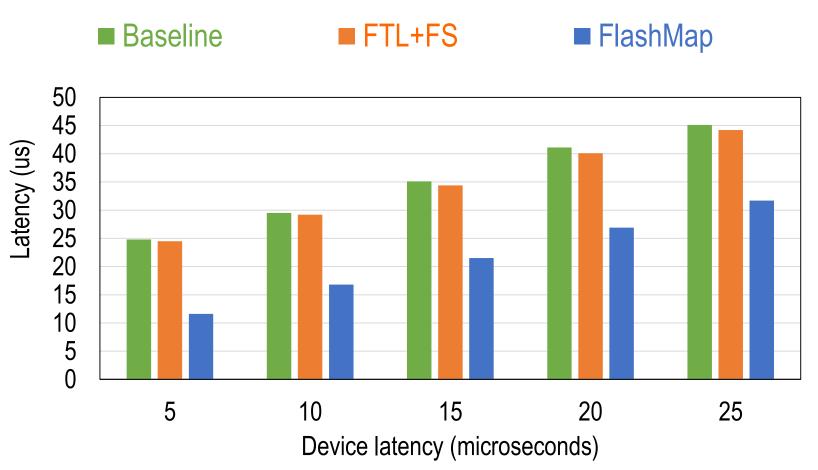

### Latency Reduction

Benefit (up to 53% latency reduction)

mainly comes from the combination of page table and file system

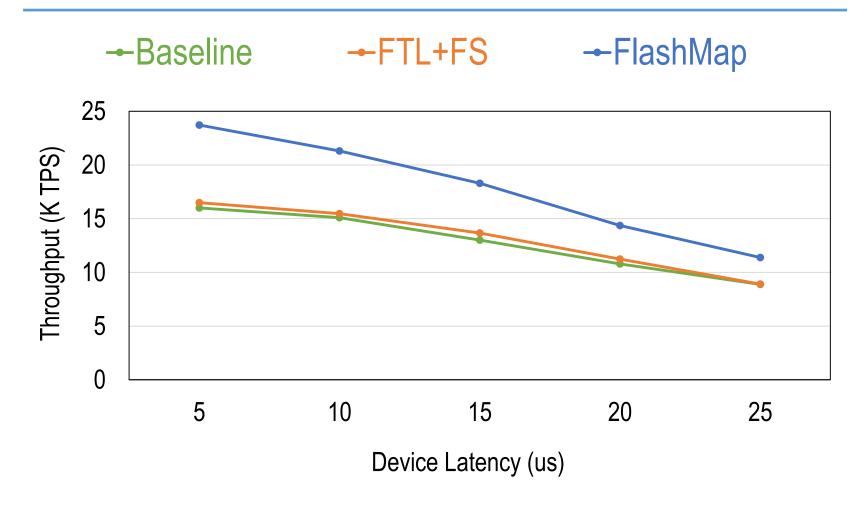

### Benefits from Reduced Latency

FlashMap: 1.8x more TPS than baseline and FTL+FS

#### Conclusion

Application

Unified Address Translation

Flash as Memory

- Reduced Storage

- 3.3x performance improvement for data-intensive applications

- Reduced Latency

- 2 53% latency reduction for high-end SSDs, 1.8x more TPS for latency-sensitive applications, e.g., database systems

# Thanks!

#### **Jian Huang**

jian.huang@gatech.edu

Anirudh Badam<sup>†</sup>

Moinuddin K. Qureshi Karsten Schwan